CXL Specification 1.0 Released: New Industry High-Speed Interconnect From Intel

by Ian Cutress on March 11, 2019 9:00 AM EST- Posted in

- CPUs

- Intel

- GPUs

- DRAM

- Interconnect

- FPGAs

- Compute Express Link

- CXL

With the battleground moving from single core performance to multi-core acceleration, a new war is being fought with how data is moved around between different compute resources. The Interconnect Wars are truly here, and the battleground just got a lot more complicated. We’ve seen NVLink, CCIX, and GenZ come out in recent years as offering the next generation of host-to-device and device-to-device high-speed interconnect, with a variety of different features. Now CXL, or Compute Express Link, is taking to the field.

This new interconnect, for which the version 1.0 specification is being launched today, started in the depths of Intel’s R&D Labs over four years ago, however what was made is being launched as an open standard, headed up by a consortium of nine companies. These companies include Alibaba, Cisco, Dell EMC, Facebook, Google, HPE, Huawei, Intel, and Microsoft, which as a collective was described as one of the companies as ‘the biggest group of influencers driving a modern interconnect standard’.

In our call, we were told that the specification is actually been in development for a few years at Intel, and was only lifted recently to drive a new consortium around an open cache coherent interconnect standard. The upcoming consortium of the nine founding companies will be incorporated later this year, working under US rules. The consortium states that members will be free to use the IP on any device, and aside from the nine founders, other companies can become contributors and/or adopters, depending on if they want to use the technology or help contribute to the next standard.

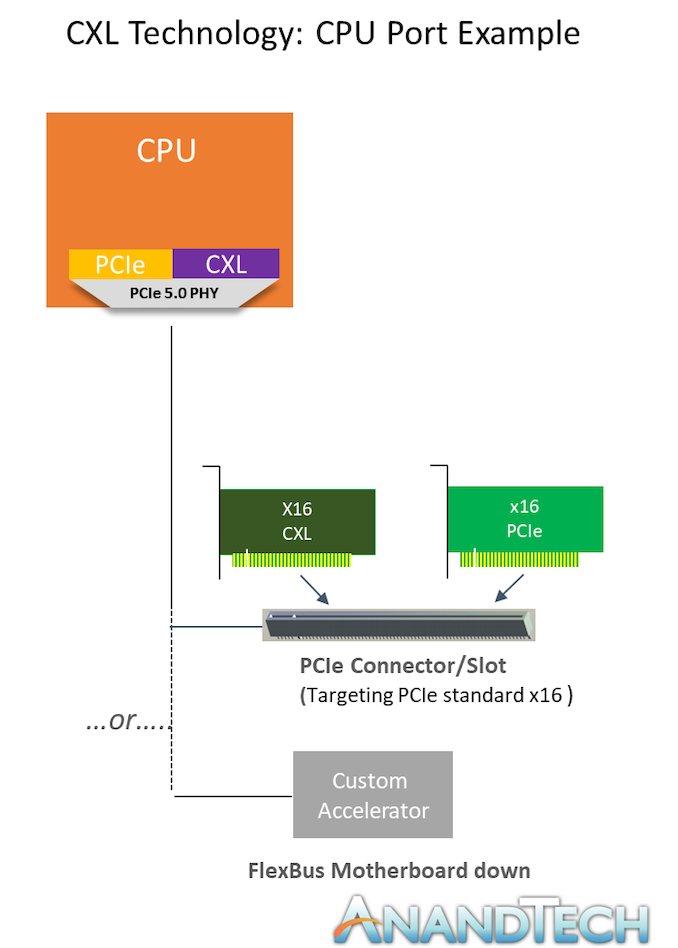

At its heart, Compute Express Link (CXL) will initially begin as a cache-coherent host-to-device interconnect, focusing on GPUs and FPGAs. It will use current PCIe 5.0 standards for physical connectivity and electrical standards, providing protocols for I/O and memory with coherency interfaces. The focus of CXL is to help accelerate AI, machine learning, media services, HPC, and cloud applications. With Intel being at the heart of this technology, we might expect to see future Intel GPUs and FPGAs connecting in a PCIe slot in ‘CXL’ mode. It will be interesting to see if this will be an additional element of the product segmentation strategy.

While some of the competing standards have 20-50+ members, the Compute Express Link actually has more founding members than PCIe (5) or USB (7). That being said however, there are a few key names in the industry missing: Amazon, Arm, AMD, Xilinx, etc. Other standards playing in this space, such as CCIX and GenZ, have common members with CXL, and when questioned on this, the comment from CXL was that GenZ made a positive comment to the CXL press release - they stated that there is a lot of synergy between CXL and GenZ, and they expect the standards to dovetail rather than overlap. It should be pointed out that Xilinx, Arm, and AMD have already stated core CCIX support, either plausible future support or in products at some level, making this perhaps another VHS / Betamax battle. The other missing company is NVIDIA, who are more than happy with NVLink and its association with IBM.

The Compute Express Link announcement is part standard and part recruitment – the as-yet consortium is looking for contributors and adopters. Other CPU architectures beyond x86 are more than welcome, with the Intel representative stating that he is happy to jump on a call to explain the company’s motivation behind the new standard. Efforts are currently underway to develop the CXL 2.0 Specification.

CXL Promoter Statements of Support

Dell EMC

“Dell EMC is delighted to be part of the CXL Consortium and its all-star cast of promoter companies. We are encouraged to see the true openness of CXL, and look forward to more industry players joining this effort. The synergy between CXL and Gen-Z is clear, and both will be important components in supporting Dell EMC’s kinetic infrastructure and this data era.”

Robert Hormuth, Vice President & Fellow, Chief Technology Officer, Server & Infrastructure Systems, Dell EMC

“Facebook is excited to join CXL as a founding member to enable and foster a standards-based open accelerator ecosystem for efficient and advanced next generation systems.”

Vijay Rao, Director of Technology and Strategy, Facebook

“Google supports the open Compute Express Link collaboration. Our customers will benefit from the rich ecosystem that CXL will enable for accelerators, memory, and storage technologies.”

Rob Sprinkle, Technical Lead, Platforms Infrastructure, Google LLC

HPE

“At HPE we believe that being able to compose compute resources over open interfaces is critical if our industry is to keep pace with the demands of a data and AI-driven future. We applaud Intel for opening up the interface to the processor. CXL will help customers utilize accelerators more efficiently and dovetails well with the open Gen-Z memory-semantic interconnect standard to aid in building fully-composable, workload-optimized systems.”

Mark Potter, HPE CTO and Director of Hewlett Packard Labs

Huawei

“Being a leading provider in the industry, Huawei will play an important role in the contribution of technology specification. Huawei’s intelligent computing products which incorporates Huawei’s chip, acceleration components and intelligent management together with innovative optimized system design, can deliver end-to-end solutions which significantly improves the rollout and system efficiency of data centers.”

Zhang Xiaohua, GM of Huawei’s Intelligent Computing BU

Intel

“CXL is an important milestone for data-centric computing, and will be a foundational standard for an open, dynamic accelerator ecosystem. Like USB and PCI Express, which Intel also co-founded, we can look forward to a new wave of industry innovation and customer value delivered through the CXL standard.”

Jim Pappas, Director of Technology Initiatives, Intel Corporation

Microsoft

“Microsoft is joining the CXL consortium to drive the development of new industry bus standards to enable future generations of cloud servers. Microsoft strongly believes in industry collaboration to drive breakthrough innovation. We look forward to combining efforts of the consortium with our own accelerated hardware achievements to advance emerging workloads from deep learning to high performance computing for the benefit of our customers.”

Dr. Leendert van Doorn, Distinguished Engineer, Azure, Microsoft

Gen-Z Consortium

“As a Consortium founded to encourage an open ecosystem for the next-generation memory and compute architectures, Gen-Z welcomes Compute Express Link (CXL) to the industry and we look forward to opportunities for future collaboration between our organizations.”

Kurtis Bowman, President, Gen-Z Consortium

48 Comments

View All Comments

Xajel - Tuesday, March 12, 2019 - link

Both PCIe 4.0 and 5.0 are already implemented in Data centers and servers, mainly the former one.In consumer, PCIe 4.0 will start this year from AMD, then maybe NV & Intel will follow. SSD makers already started working on PCIe 4.0 based SSD controllers to make use of the extra bandwidth and speed.

PCIe 4.0 requires more strict requirements than PCIe 3.0, that's why it could work on some of the current motherboard designs, so the same design can be used also for PCIe 4.0, thought it could only be for closer to the CPU connections, like only for the closest PCIe slots and to the chipsets, further distances will require additional chips (re-clockers).

PCIe 5.0 on the another hand is another thing, it even requires new motherboard materials, stricter designs for interference, distances, routes, etc.. While this is fine for data centers, these changes adds cost which is harder for consumer grade. So while PCIe 5.0 will be ready soon after PCIe 4.0, the cost will add additional barrier here. We might see PCIe 5.0 takes few more years after PCIe 4.0 in consumer products, or we might see a hybrid PCIe 5.0 & 4.0 implementation to cut costs and so on, like we already now have motherboards with both PCIe 3.0 and PCIe 2.0, we might see motherboards with both PCIe 4.0 and 3.0 in the beginning. Then after few years we will see motherboards with both PCIe 5.0 and PCIe 4.0.

eSyr - Tuesday, March 12, 2019 - link

It has been available for almost two years on the market, what else is with it?Ian Cutress - Monday, March 11, 2019 - link

1. Not Specified2. Not Specified

It's more of a 'come out of stealth' type announcement. The answers to the question 'when and how much' are often the last ones to appear.

eastcoast_pete - Monday, March 11, 2019 - link

Thanks Ian! I am a bit puzzled, though: one of the slides shown says " CXL specification 1.0 available now". I guess that's Intel speak for "we know what they are, but we won't tell you what they are or where to find them. " Open standard indeed!psychobriggsy - Monday, March 11, 2019 - link

It's probably a couple of years off, whilst CCIX (albeit PCIe 4.0) is out now.This screams of Not In Here syndrome by Intel. It looks like they will be creating their own ecosystem for their own products - FPGAs, CPUs, GPUs and so on. In the meantime CCIX will also move to PCIe 5.0 and be the non-Intel ecosystem (NV-LINK aside).

mode_13h - Monday, March 11, 2019 - link

The term I think you mean is "Not Invented Here".Can we at least be glad that they're sticking with PCIe signalling and connectivity? At least that leaves some hope of still plugging big iron accelerators into a desktop PC.

ET - Monday, March 11, 2019 - link

Anandtech is turning into the poster child of ad blockers. I don't use one, because I don't mind site owners getting some money, but having the site move from one annoying auto-running video to two, one of which is an ad which can't be even paused, is too much.Ian Cutress - Monday, March 11, 2019 - link

There should only be one video ad. If you see a second, drop an email to Ryan with a screenshot and any details you have.johnnycanadian - Monday, March 11, 2019 - link

Ian, I love Anandtech -- the depth and breadth of the content your team creates is fantastic. However, I have to agree with ET: the adverts are getting ridiculous. I captured your home page, once with uBlock and once without. The uBlock page transferred 2.3MB of data. With the adblocker turned off it was 42.4MB. That's 18.5:1 -- and I didn't even get a video ad.Please tone it down a bit and I'll gladly whitelist, as I'm sure many others.

Ian Cutress - Monday, March 11, 2019 - link

Unfortunately editorial has no control over the ads - both type and placement. It's all on our publisher. I don't get a say, although I try and make noise. I can report ads that break the site, or that are wholly inappropriate, but that's tackling specific advertisers, not the placement/arrangement.