Memory Module Technologies: TCP, EPOC and FEMMA

by Andy Hui on August 26, 2002 8:58 AM EST- Posted in

- Memory

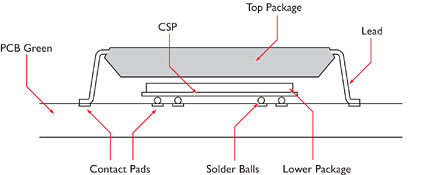

The EPOC technology mounts DRAM chips in different packages in two overlapping

rows on the printed circuit board. The top tier is a row of raised Thin-Small

Outline Package (TSOP) memory chips, and the lower tier is a row of smaller Chip

Scale Package (CSP) memory chips. There are no chip-level interconnects or

physical contact between the two overlapping rows. With the EPOC technology, the

two rows of memory chips are not in direct contact, thereby allowing airflow

in-between the top and bottom chip rows for more effective heat dissipation.

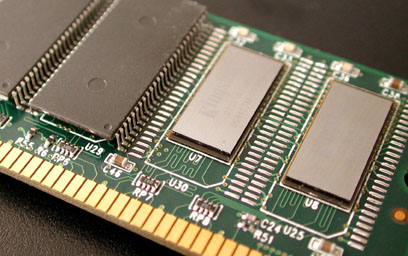

A view of the EPOC DIMM showing the CSP and the TSOP

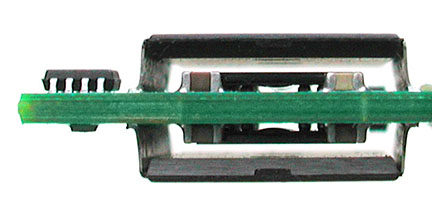

Side view of the EPOC DIMM

Kingston designed EPOC to address three issues. They set out to eliminate the

long lead-times required to stack

memory chips when using third-party stacking companies. Such lead-times impact

customer order shipments and can have significant financial impact when memory

prices fluctuate. Kingston engineers also set a design objective

requiring the new technology to be as easy to manufacture as standard modules.

The final goal was to enhance

thermal performance and overall reliability.

Kingston further says that the EPOC memory modules are an alternative to

stacked-chip modules that will enable

Kingston to stabilize the memory pricing volatility involved with third-party

chip-stacking and reduce the

production delays from weeks to days.

0 Comments

View All Comments