Sage Microelectronics To Introduce Enterprise SSD Controller Supporting STT-MRAM

by Billy Tallis on July 31, 2019 8:00 AM EST

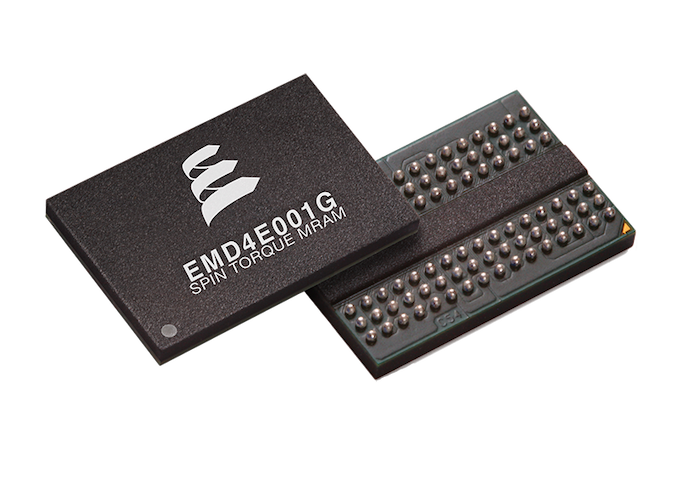

Everspin has announced that Sage Microelectronics is introducing a new enterprise SSD controller that supports Everspin's latest 1Gb magnetoresistive memory (MRAM) chips. A similar partnership between Everspin and Phison was announced last week.

Everspin's toggle MRAM is well-established as a non-volatile memory option for embedded and industrial applications, with a strong record for reliability. However, their small capacities of up to 16Mb (so far) have severely limited the potential use cases. Everspin's more recent spin-transfer torque MRAM (STT-MRAM) still can't directly compete with NAND flash on capacity, but with 1Gb parts now in production and larger parts in development, STT-MRAM is becoming useful for a new class of applications.

DDR memory controller IP that supports DRAM and Everspin's STT-MRAM is readily available, so designers of SSD controllers and other ASICs can easily add support for MRAM to products that can benefit from 1Gb or more of high-speed non-volatile memory. For SSDs, the most compelling use for MRAM is to reduce or eliminate the need for supercapacitors in enterprise SSDs. MRAM capacity is not quite high enough to entirely replace DRAM buffers in large, high-performance SSDs, but the 1Gb parts make for a decent write cache that is inherently non-volatile. Since MRAM has performance competitive with DRAM, it can be used to store FTL updates and newly written user data while still meeting the strict performance consistency requirements of enterprise SSDs.

It's not clear how much cost savings MRAM currently allows compared to a bank of supercapacitors, but Everspin and their partners cite other benefits as well: it's often much easier to fit MRAM into a small SSD form factor, and MRAM chips can outlast the useful lifespan of large capacitors, which sometimes fail before an SSD's NAND flash write endurance is exhausted.

Using DRAM, MRAM and NAND flash together in a solid state drive is not a new idea. Seagate showed prototypes at Flash Memory Summit 2017 based around Marvell controllers, and last year at FMS IBM announced a shipping product with all three types of memory and an FPGA-based controller. Now that two more controller designers are on board with the concept, it's clear that this is a viable market for Everspin if they can follow through on reducing cost per bit and continuing to increase capacities.

Everspin and Sage are both exhibiting at Flash Memory Summit next week, and we are expecting more MRAM-related announcements at the show.

Source: Everspin

4 Comments

View All Comments

abufrejoval - Wednesday, July 31, 2019 - link

As you say, form-factor could be key: Even M.2 seems feasible with that, even if most notebooks have a UPS by default. Right-sizing the capacitors just to the point where over the life-time of the product you can sustain the worst possible dirty buffer flush say with a couple of block erases ongoing at the same time, may not be trivial while capacitance is neither cheap nor small.Just the relief on the firmware designers who are asked to squeeze ever more tuples variations out of trapped electrons could be a good motive: At least the write-back cache can now be relied upon!

Diogene7 - Wednesday, July 31, 2019 - link

I know that MRAM technology is still in its early development, but I am really, really looking forward that a at least 64Gbit Spin Orbit Torque (SOT) MRAM chip (8GB) to be mass produced to replace L1 / L2 / L 3 SRAM cache and probably DRAM, for ecample in a smartphone use case : I believe it has the potential to importantly reduce software latency, which is a real pain...I believe it will be disruptive a bit like NAND flash SSD is an important improvement compared to mechanical HDD in software latency on computers...

AshlayW - Sunday, August 4, 2019 - link

Would that really have low enough latency to be useful as an L1 or even L2 cache?Santoval - Monday, October 28, 2019 - link

The fastest MRAM can reach L2 cache latencies, however only at small sizes and somewhat low densities (i.e. at older nodes). MRAM is like SRAM in some sense : as its size increases its latency starts deteriorating, quite fast. While MRAM *could* replace L2 & L3 cache at an equivalent latency (and possibly at a quite larger size due to its much higher density than 6T-SRAM) I am not sure if Everspin's STT-MRAM specific variant could do it. In any case L1 cache is off limits.