ARM's Cortex A57 and Cortex A53: The First 64-bit ARMv8 CPU Cores

by Anand Lal Shimpi on October 30, 2012 11:58 AM EST- Posted in

- CPUs

- IT Computing

- Arm

- Cloud Computing

- SoCs

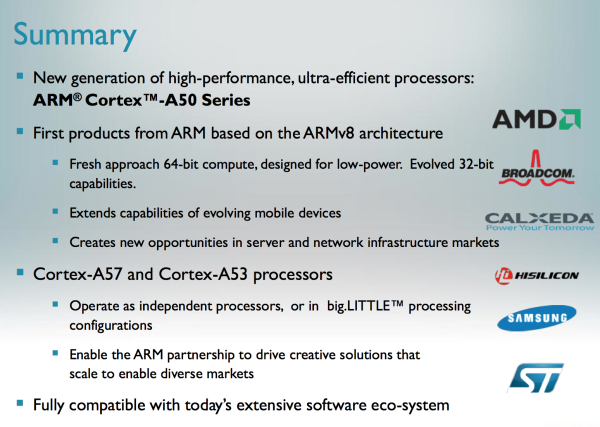

Yesterday AMD revealed that in 2014 it would begin production of its first ARMv8 based 64-bit Opteron CPUs. At the time we didn't know what core AMD would use, however today ARM helped fill in that blank for us with two new 64-bit core announcements: the ARM Cortex-A57 and Cortex-A53.

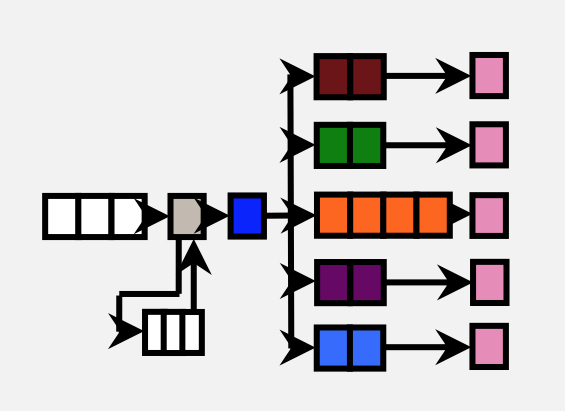

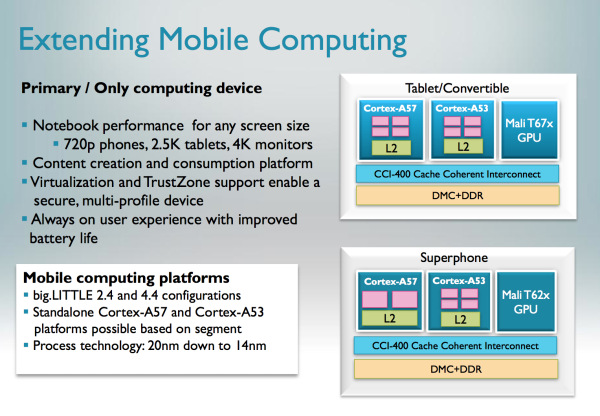

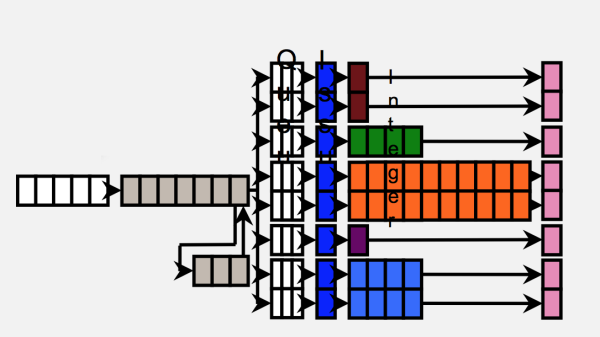

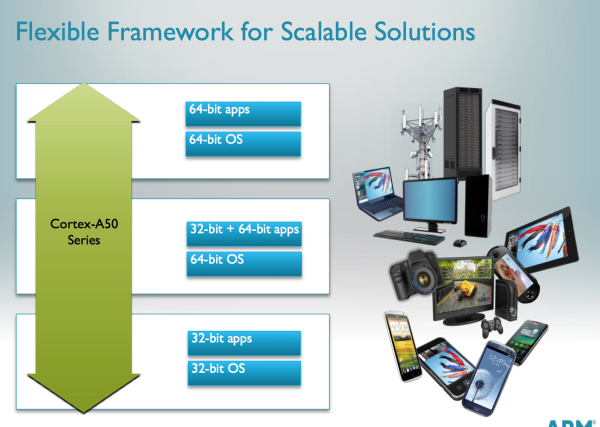

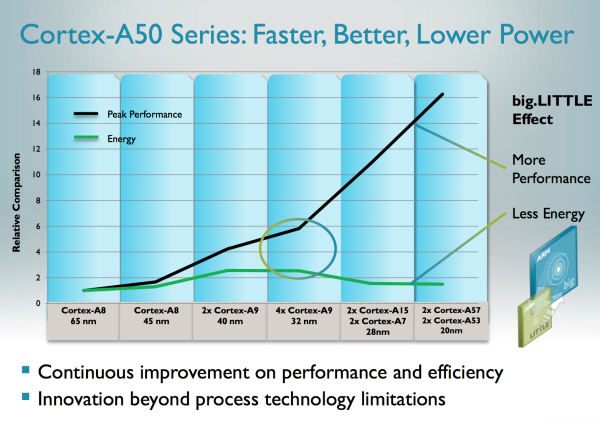

You may have heard of ARM's Cortex-A57 under the codename Atlas, while A53 was referred to internally as Apollo. The two are 64-bit successors to the Cortex A15 and A7, respectively. Similar to their 32-bit counterparts, the A57 and A53 can be used independently or in a big.LITTLE configuration. As a recap, big.LITTLE uses a combination of big (read: power hungry, high performance) and little (read: low power, lower performance) ARM cores on a single SoC.

By ensuring that both the big and little cores support the same ISA, the OS can dynamically swap the cores in and out of the scheduling pool depending on the workload. For example, when playing a game or browsing the web on a smartphone, a pair of A57s could be active, delivering great performance at a high power penalty. On the other hand, while just navigating through your phone's UI or checking email a pair of A53s could deliver adequate performance while saving a lot of power. A hypothetical SoC with two Cortex A57s and two Cortex A53s would still only appear to the OS as a dual-core system, but it would alternate between performance levels depending on workload.

Architecturally, the Cortex A57 is much like a tweaked Cortex A15 with 64-bit support. The CPU is still a 3-wide/3-issue machine with a 15+ stage pipeline. ARM has increased the width of NEON execution units in the Cortex A57 (128-bits wide now?) as well as enabled support for IEEE-754 DP FP. There have been some other minor pipeline enhancements as well. The end result is up to a 20 - 30% increase in performance over the Cortex A15 while running 32-bit code. Running 64-bit code you'll see an additional performance advantage as the 64-bit register file is far simplified compared to the 32-bit RF.

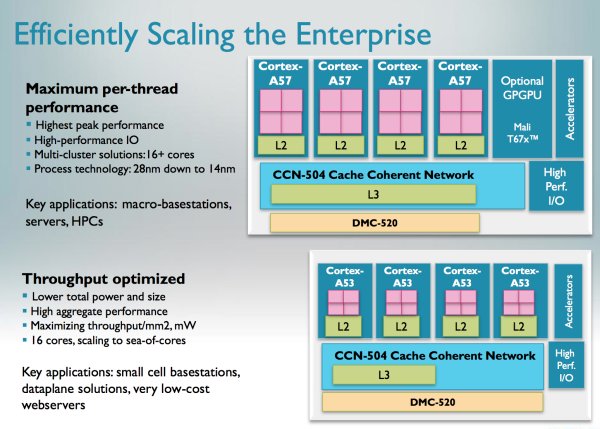

The Cortex A57 will support configurations of up to (and beyond) 16 cores for use in server environments. Based on ARM's presentation it looks like groups of four A57 cores will share a single L2 cache.

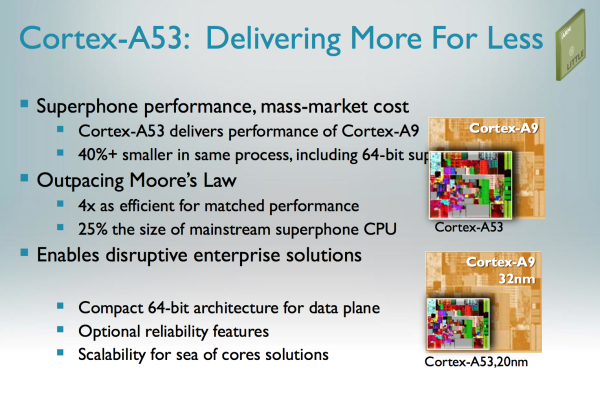

ARM's Cortex A53

Similarly, the Cortex A53 is a tweaked version of the Cortex A7 with 64-bit support. ARM didn't provide as many details here other than to confirm that we're still looking at a simple, in-order architecture with an 8 stage pipeline. The A53 can be used in server environments as well since it's ISA compatible with the A57.

ARM claims that on the same process node (32nm) the Cortex A53 is able to deliver the same performance as a Cortex A9 but at roughly 60% of the die area. The performance claims apply to both integer and floating point workloads. ARM tells me that it simply reduced a lot of the buffering and data structure size, while more efficiently improving performance. From looking at Apple's Swift it's very obvious that a lot can be done simply by improving the memory interface of ARM's Cortex A9. It's possible that ARM addressed that shortcoming while balancing out the gains by removing other performance enhancing elements of the core.

Both CPU cores are able to run 32-bit and 64-bit ARM code, as well as a mix of both so long as the OS is 64-bit.

Completed Cortex A57 and A53 core designs will be delivered to partners (including AMD and Samsung) by the middle of next year. Silicon based on these cores should be ready by late 2013/early 2014, with production following 6 - 12 months after that. AMD claimed it would have an ARMv8 based Opteron in production in 2014, which seems possible (although aggressive) based on what ARM told me.

ARM expects the first designs to appear at 28nm and 20nm. There's an obvious path to 14nm as well.

It's interesting to note ARM's commitment to big.LITTLE as a strategy for pushing mobile SoC performance forward. I'm curious to see how the first A15/A7 designs work out. It's also good to see ARM not letting up on pushing its architectures forward.

117 Comments

View All Comments

Khato - Tuesday, October 30, 2012 - link

Oh, so all the current ARM chips used in tablets are 'more like a netbook chip with a 6 cell battery alongside' then? Good to know.http://www.anandtech.com/show/6340/intel-details-a...

Feel free to disregard the power consumption numbers, since clearly Intel can't be trusted to provide realistic numbers on testing they know review sites will be able replicate once the platform's launched.

Klimax - Wednesday, October 31, 2012 - link

300 a chip? Why do you quote cost for LGA2011-like platform(entry level)?In reality it's 50+ range. Are you trying to FUD?

wsw1982 - Wednesday, October 31, 2012 - link

Arm will not be comparable with haswell but with Atom.Kurge - Thursday, November 1, 2012 - link

Lolwut? ARM is moving up to the 5W range with its bigger ARM chips. Haswell will have a 10W part, maybe even lower.It's silly to think Intel won't push Broadwell down to ~5W. So on the high end ARM will be competing with Core chips, which is a battle it can't hope to win.

On the low end, it'll be Atom but it's not like Medfield will be what's used in 2014.

ImSpartacus - Tuesday, October 30, 2012 - link

To be honest, I want to keep Intel sweating.A5 - Tuesday, October 30, 2012 - link

Yeah. Intel is at its best when they have to really compete.B1gBOY - Tuesday, October 30, 2012 - link

Not only Intel. If you think about it, Anandtech EIC must be sweating too...You know what i mean...bengildenstein - Tuesday, October 30, 2012 - link

When hearing "3x performance at 0.25 the size," it feels eerily close to the same tech strategy as Imaginations Meta CPU core. For the uninitiated, the Meta core eschews out-of-order operations, and instead adopts an in-order multi-threaded approach which gives a significant bump in performance for cache-miss scenarios when spread over multiple cores, but is radically more simple than traditional ooo cores (hence the reduction in die space).blanarahul - Tuesday, October 30, 2012 - link

Now AMD's announcement makes sense.blanarahul - Tuesday, October 30, 2012 - link

Hmmmmm. Now we all know what Galaxy S5 will have. And what Qualcomm is working on (Snapdragon S5).