Intel to Revive ‘Tick-Tock’ Model, Unquestioned CPU Leadership Performance in 2024/2025

by Dr. Ian Cutress on March 23, 2021 6:31 PM EST- Posted in

- CPUs

- Intel

- Tick-Tock

- 7nm

- Chiplets

- Pat Gelsinger

- Meteor Lake

- Tiles

As part of today’s announcements, during Intel’s Q&A session after the prepared remarks, CEO Pat Gelsinger explained how Intel is going to revive its fortunes when it comes to its leading edge compute products. One of Gelsinger’s mantras seems to be that unquestioned leadership products bring unquestioned leadership margins for those products, and for Intel to execute, it needs to return to its days of old.

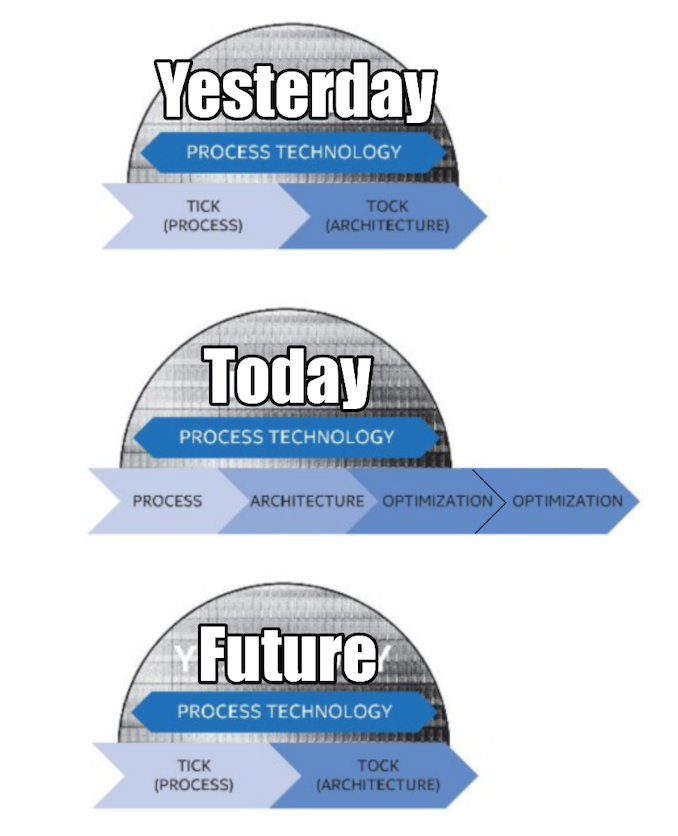

In the past, through the 1990s, 2000s, and into the 2010s, Intel’s manufacturing philosophy was known as ‘Tick-Tock’. This means that for every product generation, the leading edge compute hardware was either a Tick (process node enhancement), or a Tock (microarchitecture enhancement). Each generation would alternate between the two, allowing Intel to take advantage of a familiar design on a new process node, or using a mature node to enable a new performance-focused design. That policy was scuppered when delays to Intel’s 10nm forced Intel into more of a Tick-Tock-Optimization-Optimization-Optimization model.

Today CEO Pat Gelsinger stated that at Intel’s core it has to re-establish the Tick-Tock model that enabled repeated leadership in the CPU ecosystem, buoyed by a healthy CPU roadmap. Part of this is re-establishing discipline in Intel’s ranks to continually provide both microarchitecture updates and process node updates on a regular expected cadence. Pat stated as part of the call that Intel will look towards a confirmed yearly process node improvement, and as a result, there might be a lot of Ticks in the future, with a push to more Tocks as well.

On top of this commentary, Pat Gelsinger also stated that Intel’s CPU roadmaps are already baked in through 2021, 2022, and 2023. The company is thus looking to 2024/2025 for ‘unquestioned CPU leadership performance’, which traditionally means the fastest processor for single thread and multi-thread workloads. This is for sure a laudable goal, however Intel will also have to adapt to a changing landscape of chiplet processor designs (coming in 2023), enhancing on-die accelerators (GNA already present), and also what it means to have leadership performance – in the modern era, leadership performance doesn’t mean much if you’re also pushing lots of Watts. Intel stated that its 7nm process is now comfortably on track to deliver Meteor Lake, a client CPU using tiles/chiplets, in 2023, however we are likely looking to a 7nm variant or even external processes for a 2024/2025 product. Intel has also stated that it is looking to consider the core of its leading edge compute on external foundry processes, although one might argue that this doesn’t explicitly say ‘CPU’.

It is also worth noting that Intel/Gelsinger isn’t calling its disaggregated silicon as ‘chiplets’, and prefers to use the term ‘tiles’. This is because Intel’s tiles amount to long wires across 3D packaging technologies like EMIB and Foveros, compared to package-based multi-die interconnect that require buffers as well as control fabric. Tiles by this definition are more costly to implement than chiplets, and have additional thermal considerations by having high-powered silicon close together, so it will be interesting to see how Intel balances these new packaging technologies with the more cost-sensitive elements of its portfolio, such as client processors.

It’s been known that Intel’s microarchitecture teams haven’t been idle waiting for 10nm to come through the pipe, with a number of designs ready and waiting to go for when the process node technology matures. With any luck, if Intel can get a headwind with 7nm, when 2024 rolls around it might all come thick and fast.

109 Comments

View All Comments

GeoffreyA - Friday, March 26, 2021 - link

No doubt, Mr. Keller is a brilliant mind.Oxford Guy - Wednesday, March 31, 2021 - link

'Bulldozer was a bad architecture and it succeeded in getting process node upgrades.'No. The high-performance desktop and supercomputer areas were never upgraded after Piledriver, which has 2011 stamped on the spreaders.

That was a long time to wait for Zen 1.

Railander - Tuesday, March 23, 2021 - link

to be fair, i don't remember AMD making claims as ambitious as these when they were developing zen.Otritus - Wednesday, March 24, 2021 - link

AMD made a claim of a 40% IPC uplift in a single generation on a brand new node with a massive improvement in efficiency, which is pretty damn ambitious.Sunny cove had an IPC lead over Zen 2, so it is likely that Golden Cove will have an IPC lead. over Zen 3. If this pattern follow in 3-4 years Intel will have a new microarchitecture leading Zen 4, and possibly releasing their next one that leads Zen 5.

Intel has performance now, but tremendously lacks efficiency with 14nm. If 7nm is as good as Intel claims it is, then it is likely that Intel could be back in the efficiency and IPC lead (also if 7nm is that good then Intel can hit 5+ Ghz, giving them the single thread performance crown). With "tiles" Intel could combat AMD's chiplets, taking the multi-threaded crown.

With this in mind, I don't think Intel is as ambitious as AMD for Zen. Remember AMD went from a waste of silicon to viable to leader. Intel plans to go from viable to leader, which isn't that hard for a company of their scope (as long as there is good management).

grant3 - Wednesday, March 24, 2021 - link

Great take. Despite Intel's recent failures, it still commands massive resources. It's entirely up to management.Spunjji - Friday, March 26, 2021 - link

"If 7nm is as good as Intel claims it is"That's the big "if". They claimed 10nm was great long past the point where it was clear it wasn't even hitting their claimed density, let alone performance. That's no reason to assume 7nm is as bad as 10nm, but it does give me pause on taking their word on how good it is.

They can do 5Ghz on 10nm now, albeit at a rather ugly point on the voltage/power curve. I'll be interested to see whether that gets better or worse with 7nm.

whatthe123 - Friday, March 26, 2021 - link

They screwed up on EUV timing in both cases. Their new CEO seems more willing and interested in branching out and using standardized tools, rather than going all custom while making crazy speculative goals like they did under people like Krzanich. 7nm will depend a lot on how quickly they can adopt EUV and if they can even get enough EUV equipment to hit their volume targets. I'd say its doable but not under their old corporate culture, going to need a lot of money and sleepless nights.Oxford Guy - Saturday, March 27, 2021 - link

AMD was coming from a garbage architecture on a garbage node (28nm bulk, density-optimized not performance-optimized, with the sloppy FM socket standard).Not difficult to make a massive improvement from that.

Had AMD aggressively improved upon Phenom, rather than releasing Bulldozer (which had worse, not better, IPC) — and had the company not decided to leave the architecture blowing in the wind (an architecture that was far too slow in 2011) until Zen it wouldn't have been able to make such a great improvement. Remember, not only did AMD refuse to improve upon Piledriver (basically Bulldozer with minor tweaks, including the breaking of AVX) for the 'performance desktop' and supercomputer markets, it cut the number of cores way down for Steamroller and Excavator. AND, it cut cache size to the bone. All of that was to make them cheap to produce, not performant. AMD could have taken the improvements from Steamroller and Excavator, married them to the 32nm SOI node rather than 28nm dense-library and the anemic FM socket, and further improved the 'construction core/CMT' design. It didn't do that. The company left it completely stagnant, an architecture that was mostly dead on arrival in 2011, as it wasn't fast enough versus Phenom and was destroyed by Sandy Bridge quads that had far fewer transistors and much less power consumption.

AMD would have only looking better with Zen had the previous architecture been something from VIA.

GeoffreyA - Sunday, March 28, 2021 - link

"density-optimized not performance-optimized"It reduced area, yes, but more importantly, dropped power consumption. And if I had been AMD, I think I would have done exactly the same, concerning Steamroller and Excavator, knowing that Zen was almost ready to knock Intel from its high horse.

Oxford Guy - Wednesday, March 31, 2021 - link

It also reduced maximum clocks — the thing that entire architecture hinged on.